# DNP/5280 Revision 1.21 – User Information

The DIL/NetPC DNP/5280 provides a very compact ColdFire-based low power embedded controller (Motorola 32-bit MCF5280) with TCP/IP stack and Web server for high-speed embedded networking applications. The main features are:

- ColdFire Microcontroller MCF5280 with 66 MHz Clock Speed

- 128 Mbit (16 Mbytes) SDRAM MT48LC4M32B2 with 32-bit Data Bus

- 64 Mbit (8 Mbytes) Flash Am29LV640 with 16-bit Data Bus

- 10/100 Mbps Ethernet PHY RTL8201 (25 MHz Clock Source)

The DIL/NetPC offers the footprint of a standard 64-pin DIL socket with 2.54mm centers and all the hardware and software features necessary to add high-speed networking capabilities to any product design. The DIL/NetPC is developed specifically for products that need to be connected to 10 or 100 Mbps Ethernet-based TCP/IP networks with minimum development costs.

Figure 1: The DIL/NetPC DNP/5280 with a ColdFire MCF5280 Microcontroller

The DIL/NetPC DNP/5280 is a ready-to-run full programmable 32-bit embedded networking system. The use of the DNP/5280 will allow you to realize substantial time and costs savings over other chip-based approaches. Currently, there is no other 10/100 Mbps Ethernet- and TCP/IP-based embedded networking solution with more development time savings on the market. There is also no faster Time-to-Market for your product with lower costs if 32-bit-based 10/100 Mbps Ethernet, full TCP/IP and a embedded Web server or other TCP/IP-based server software is required.

To interface the DNP/5280 with existing devices and equipment, the DNP/5280

offers two asynchronous serial RS232C interfaces with TTL levels and handshake signals, I2C interchip bus interface, queued SPI (Serial Peripheral Interface), CAN interface with support for the CAN protocol specification 2.0B, 20-bit general purpose high-speed parallel I/Os and a 8-bit extension bus with interrupt inputs and chip select outputs.

There are two ways for DNP/5280 integration: 1. Adapt the DNP/5280 to your existing product. Use the existing I/Os within your product to communicate with the DNP/5280. 2. Use the DNP/5280 to control and monitor the hardware of your existing product. This might enable you to replace your existing controller entirely. In a new product design, the DNP/5280 can be the main controller. Additional I/Os are driven by the 8-bit extension bus.

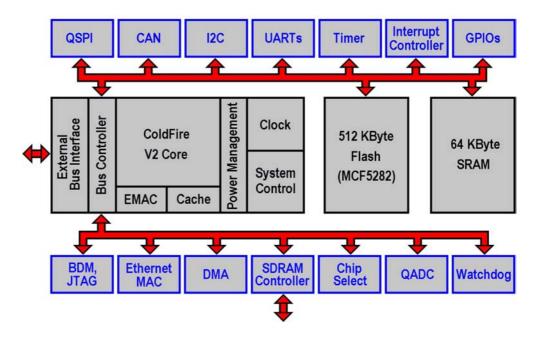

#### The Motorola ColdFire MCF5280 Microcontroller

The MCF5282 is the first microcontroller based on Motorola's 32-bit ColdFire core integrated with Ethernet, Flash and CAN. This device offers advanced communications features, a rich peripheral set and a variety of supporting software and development tools.

Figure 2: MCF5280/MCF5282 Block Diagram

The MCF5282 is designed to simplify embedded Ethernet-networked micro-controller applications. With its integrated 10/100 Mbps Ethernet MAC and network-ready applications software, the MCF5282 can bring standards-based networking to a variety of traditional MCU applications including food service equipment, security systems, vending machines, exercise equipment and industrial controllers. Applications in all of these areas will benefit from networking functions such as Web-based user interfaces, network time synchronization, and router/gateway functionality for legacy serial protocols. The MCF5282 main features are:

- V2 ColdFire core delivering 54 (Dhrystone 2.1) MIPS at 66 MHz running from internal Flash (max from Cache/RAM 63 MIPS)

- 512KB embedded Flash memory (only the MCF5282, not the MCF5280)

- Enhanced Multiply-Accumulate Unit (eMAC) for DSP functionality

- 64 Kbytes of static RAM

- 10/100 Ethernet MAC

- Cache for external access support

- Address decode and chip selects

- CAN 2.0B controller area network interface with 16 message buffers

- Three UARTs with DMA capability

- Queued serial peripheral interface (QSPI) with four peripheral chip selects

- 8-channel 10-bit queued analog-to-digital converter (QADC)

- Four 32-bit timers with capture, compare and DMA capability

- Eight 16-bit timer channels for capture, compare, and pulse width modulation

- Four periodic interrupt timers (PITs)

- I2C bus controller

- JTAG for board testing

- BDM for debug, including real-time trace

- 17 mm x 17 mm x 1.6 mm 256-ball MAPBGA package

- Operation at 66 MHz from -40C to +85C

Some MCF528x feature are not accessible with the DIL/NetPC DNP/5280. The main reason for that is the DIL-64 connector and the pin-out compatibility to other DIL/NetPCs with DIL-64 connectors.

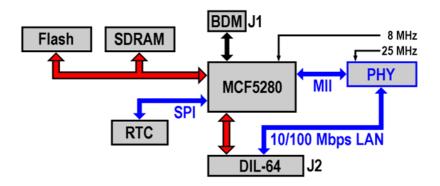

## The DIL/NetPC DNP/5280 Block Diagram

The DIL/NetPC DNP/5280 is build around Motorola's 32-bit ColdFire MCF5280/MCF5282 microcontroller unit (MCU) running with 66 MHz. The external main components around the ColdFire are one Flash memory chip with 8 Mbytes, one 16-MByte SDRAM memory chip, and one 10/100 Mbps Ethernet PHY (the Ethernet MAC is a part of the ColdFire MCU).

Figure 3: DIL/NetPC DNP/5280 Block Diagram

The DIL/NetPC DNP/5280 LAN interface is equipped with four small on-board LEDs. Table 1 offers a overview.

| Name | Function |                                     |

|------|----------|-------------------------------------|

| LED0 | Link     | Ethernet Cable Connection available |

| LED1 | Duplex   | Duplex Mode                         |

| LED2 | 10Act    | 10 Mbps LAN Traffic                 |

| LED3 | 100Act   | 100 Mbps LAN Traffic                |

Table 1: DNP/5280 LAN LEDs

The 66 MHz clock speed of the DIL/NetPC DNP/5280 comes from a 8 MHz clock source.

The DNP/5280 offers only two connectors: J1 (BDM Interface) and J2 (64-pin DIL Connector). Table 2 and Table 4 of this document show the pinout.

#### **Pinout J1: BDM Connector (J0501)**

| Pin | Name                      | Remarks      |

|-----|---------------------------|--------------|

| 1   | VIO (3.3 VDC I/O Voltage) |              |

| 2   | GND                       |              |

| 3   | TA#                       | BDM Function |

| 4   | BKPT#                     | BDM Function |

| 5   | Reset#                    | BDM Function |

| 6   | DSCLK#                    | BDM Function |

| 7   | DSI#                      | BDM Function |

| 8   | TCLK                      | BDM Function |

| 9   | PST3                      | BDM Function |

| 10  | DS0                       | BDM Function |

| 11  | PST2                      | BDM Function |

| 12  | DDATA3                    | BDM Function |

| 13  | PST1                      | BDM Function |

| 14  | DDATA2                    | BDM Function |

| 15  | PST0                      | BDM Function |

| 16  | DDATA1                    | BDM Function |

| 17  | PSTCLK                    | BDM Function |

| 18  | DDATA0                    | BDM Function |

| 19  | GND                       |              |

| 20  | RCM                       | GPTB3        |

Table 2: J1 Pinout (DNP/5280 BDM Connector)

**Please note:** Pin 20 (RCM = Remote Console Mode) of connector J1 is a jumper position point. The DNP/5280 allows you to connect this pin with the help of a small 2 mm jumper bridge to pin 19 (GND) of connector J1.

RCM is direct connected to pin T12 (GPTB3) of the Motorola 32-bit ColdFire MCF5280/MCF5282 microcontroller. There is also a 4700 Ohms resistor to 3.3 VDC on-board for pulling GPTB3 to Vcc (GPTB3 = 1) if no jumper bridge available.

| Pin 19 – Pin 20      | Status           |

|----------------------|------------------|

| Jumper not available | GPTB3 = 1 (High) |

| Jumper available     | GPTB3 = 0 (Low)  |

**Table 3:** The RCM Jumper Modes

The DNP/5280 default boot loader and ROM monitor program dBUG checks RCM at power-up. If no jumper bridge is available (GPTB3 = 1), dBUG is running the uClinux image from Flash memory. If dBUG detects a jumper bridge from pin 19 to pin 20, this program enters a command mode.

## Pinout J2: DIL-64 Connector (J0901)

| Pin | Name  | Function                    |

|-----|-------|-----------------------------|

| 1   | PA0   | Parallel I/O, Port A, Bit 0 |

| 2   | PA1   | Parallel I/O, Port A, Bit 1 |

| 3   | PA2   | Parallel I/O, Port A, Bit 2 |

| 4   | PA3   | Parallel I/O, Port A, Bit 3 |

| 5   | PA4   | Parallel I/O, Port A, Bit 4 |

| 6   | PA5   | Parallel I/O, Port A, Bit 5 |

| 7   | PA6   | Parallel I/O, Port A, Bit 6 |

| 8   | PA7   | Parallel I/O, Port A, Bit 7 |

| 9   | PB0   | Parallel I/O, Port B, Bit 0 |

| 10  | PB1   | Parallel I/O, Port B, Bit 1 |

| 11  | PB2   | Parallel I/O, Port B, Bit 2 |

| 12  | PB3   | Parallel I/O, Port B, Bit 3 |

| 13  | PB4   | Parallel I/O, Port B, Bit 4 |

| 14  | PB5   | Parallel I/O, Port B, Bit 5 |

| 15  | PB6   | Parallel I/O, Port B, Bit 6 |

| 16  | PB7   | Parallel I/O, Port B, Bit 7 |

| 17  | PC0   | Parallel I/O, Port C, Bit 0 |

| 18  | PC1   | Parallel I/O, Port C, Bit 1 |

| 19  | PC2   | Parallel I/O, Port C, Bit 2 |

| 20  | PC3   | Parallel I/O, Port C, Bit 3 |

| 21  | RXD1  | COM1 Serial Port, RXD Pin   |

| 22  | TXD1  | COM1 Serial Port, TXD Pin   |

| 23  | CTS1  | COM1 Serial Port, CTS Pin   |

| 24  | RTS1  | COM1 Serial Port, RTS Pin   |

| 25  | DCD1  | COM1 Serial Port, DCD Pin   |

| 26  | DSR1  | COM1 Serial Port, DSR Pin   |

| 27  | DTR1  | COM1 Serial Port, DTR Pin   |

| 28  | RI1   | COM1 Serial Port, RI Pin    |

| 29  | RESIN | RESET Input                 |

| 30  | TX+   | 10/100 Mbps LAN, TX+ Pin    |

| 31  | TX-   | 10/100 Mbps LAN, TX- Pin    |

| 32  | GND   | Ground                      |

**Table 4.A:** J2 Pins 1 to 32

| Pin | Name    | Function                  |

|-----|---------|---------------------------|

| 33  | RX+     | 10/100 Mbps LAN, RX+ Pin  |

| 34  | RX-     | 10/100 Mbps LAN, RX- Pin  |

| 35  | RESOUT  | RESET Output              |

| 36  | VBAT    | Real-Time Clock Battery   |

| 37  | CLKOUT  | Clock Output              |

| 38  | TXD2    | COM2 Serial Port, TXD Pin |

| 39  | RXD2    | COM2 Serial Port, RXD Pin |

| 40  | INT5    | Interrupt Input 5         |

| 41  | INT4    | Interrupt Input 4         |

| 42  | INT3    | Interrupt Input 3         |

| 43  | INT2    | Interrupt Input 2         |

| 44  | INT1    | Interrupt Input 1         |

| 45  | CS4     | Chip Select Output 4      |

| 46  | CS3     | Chip Select Output 3      |

| 47  | CS2     | Chip Select Output 2      |

| 48  | CS1     | Chip Select Output 1      |

| 49  | IOCHRDY | I/O Channel Ready         |

| 50  | IOR     | I/O Read Signal           |

| 51  | IOW     | I/O Write Signal          |

| 52  | SA3     | Address Bit 3             |

| 53  | SA2     | Address Bit 2             |

| 54  | SA1     | Address Bit 1             |

| 55  | SA0     | Address Bit 0             |

| 56  | SD7     | Data Bit 7                |

| 57  | SD6     | Data Bit 6                |

| 58  | SD5     | Data Bit 5                |

| 59  | SD4     | Data Bit 4                |

| 60  | SD3     | Data Bit 3                |

| 61  | SD2     | Data Bit 2                |

| 62  | SD1     | Data Bit 1                |

| 63  | SD0     | Data Bit 0                |

| 64  | VCC     | 3.3 Volt Power Input      |

**Table 4.B:** J2 Pins 33 to 64

#### **Function Multiplexing of the DIL-64 Connector**

Some pins at the DIL/NetPC DNP/5280 DIL-64 connector J2 are multifunction pins with a primary function and a secondary function. The default use is identical to the primary function.

| Pin | Name | <b>Primary Function</b>     | <b>Secondary Function</b> |

|-----|------|-----------------------------|---------------------------|

| 13  | PB4  | Parallel I/O, Port B, Bit 4 | SCL (I2C)                 |

| 14  | PB5  | Parallel I/O, Port B, Bit 5 | SDA (I2C)                 |

| 15  | PB6  | Parallel I/O, Port B, Bit 6 | CANTX (CAN)               |

| 16  | PB7  | Parallel I/O, Port B, Bit 7 | CANRX (CAN)               |

| 17  | PC0  | Parallel I/O, Port C, Bit 0 | QSPIDO (SPI)              |

| 18  | PC1  | Parallel I/O, Port C, Bit 1 | QSPIDI (SPI)              |

| 19  | PC2  | Parallel I/O, Port C, Bit 2 | QSPICLK (SPI)             |

| 20  | PC3  | Parallel I/O, Port C, Bit 3 | QSPICS0 (SPI)             |

Table 5: Multifunction Pins of the DNP/5280 DIL-64 Connector

The primary function of the pins shown at Table 5 is identical to the DIL/NetPC DIL-64 standard pinout. This pin functions are compatible to other DIL/NetPCs with DIL-64 connectors. The secondary functions are ColdFire-specific.

#### **PIO Pin Mapping**

The bits of the DNP/5280 20-bit PIO (Parallel Input Output Port) are directly connected to signals of the Motorola MCF5280 ColdFire 32-bit microcontroller. The following table shows this mapping. Please see also the *MCF5282 ColdFire Microcontroller User's Manual R.O.1* (MCF5282UM/D) for the MCF5280 pin function details.

| Pin | Name | MCF5280 Pin Function | MCF5280 Pin |

|-----|------|----------------------|-------------|

| 1   | PA0  | AN52                 | R4          |

| 2   | PA1  | AN53                 | T4          |

| 3   | PA2  | AN55                 | P3          |

| 4   | PA3  | AN56                 | R3          |

| 5   | PA4  | AN0                  | T3          |

| 6   | PA5  | AN1                  | R2          |

| 7   | PA6  | AN2                  | T2          |

| 8   | PA7  | AN3                  | R1          |

| 9   | PB0  | GPTA0                | N13         |

| 10  | PB1  | GPTA1                | P13         |

| 11  | PB2  | GPTA2                | R13         |

| 12  | PB3  | GPTA3                | T13         |

| 13  | PB4  | SCL                  | E15         |

| 14  | PB5  | SDA                  | E14         |

| 15  | PB6  | CANTX                | E13         |

| 16  | PB7  | CANRX                | D16         |

| 17  | PC0  | QSPIDO               | F13         |

| 18  | PC1  | QSPIDI               | E16         |

| 19  | PC2  | QSPICLK              | F14         |

| 20  | PC3  | QSPICS0              | F15         |

Table 6: DNP/5280 PIO Pin Mapping to MCF5280 Pins

#### **COM Port Pin Mapping**

The 10 pins of the two DIL/NetPC DNP/5280 UARTs (Serial Ports COM1 and COM2) are direct connected to signals of the Motorola MCF5280 ColdFire 32-bit microcontroller. The following table shows this mapping.

| Pin | Name | MCF5280 Pin Funktion | MCF5280 Pin | Source |

|-----|------|----------------------|-------------|--------|

| 21  | RXD1 | URXD0                | N6          | UART   |

| 22  | TXD1 | UTXD0                | T7          | UART   |

| 23  | CTS1 | DTOUT0               | J13         | UART   |

| 24  | RTS1 | DTOUT1               | J15         | UART   |

| 25  | DCD1 | DTOUT2               | K13         | GPIO   |

| 26  | DSR1 | DTIN2                | K14         | GPIO   |

| 27  | DTR1 | DTOUT3               | K15         | GPIO   |

| 28  | RI1  | DTIN3                | K16         | GPIO   |

|     |      |                      |             |        |

| 38  | TXD2 | UTXD1                | P7          | UART   |

| 39  | RXD2 | URXD1                | R7          | UART   |

Table 7: DNP/5280 COM Port Pin Mapping to MCF5280 Pins

Please see also the *MCF5282 ColdFire Microcontroller User's Manual R.0.1* (MCF5282UM/D) for the MCF5280 pin function details.

#### **Bus Signal Mapping (8-bit I/O Expansion Bus)**

The 27 pins of the DNP/5280 8-bit I/O Expansion Bus are directly connected to signals of the Motorola MCF5280 ColdFire 32-bit microcontroller. The following table shows this mapping.

Please see also the *MCF5282 ColdFire Microcontroller User's Manual R.0.1* (MCF5282UM/D) for the MCF5280 pin function details.

| Pin | Name    | MCF5280 Pin Funktion | MCF5280 Pin | Remarks |

|-----|---------|----------------------|-------------|---------|

| 29  | RESIN   | RESET                | R11         | 1       |

|     |         |                      |             |         |

| 35  | RESOUT  | RSTOUT#              | P11         | 1       |

|     |         |                      |             |         |

| 37  | CLKOUT  | CLKOUT               | N7          | 1       |

|     |         |                      |             |         |

| 40  | INT5    | IRQ7                 | B15         |         |

| 41  | INT4    | IRQ6                 | B16         |         |

| 42  | INT3    | IRQ5                 | C14         |         |

| 43  | INT2    | IRQ4                 | C15         |         |

| 44  | INT1    | IRQ3                 | C16         |         |

| 45  | CS4     | RAS1#                | H13         | 1       |

| 46  | CS3     | CS3#                 | L16         |         |

| 47  | CS2     | CS2#                 | L15         |         |

| 48  | CS1     | CS1#                 | L14         |         |

| 49  | IOCHRDY | TA#                  | P16         |         |

| 50  | IOR     | OE#                  | N16         |         |

| 51  | IOW     | R/W#                 | N15         |         |

| 52  | SA3     | A3                   | E3          |         |

| 53  | SA2     | A2                   | E4          |         |

| 54  | SA1     | A1                   | F1          |         |

| 55  | SA0     | A0                   | F2          |         |

| 56  | SD7     | D31                  | F3          |         |

| 57  | SD6     | D30                  | G1          |         |

| 58  | SD5     | D29                  | G2          |         |

| 59  | SD4     | D28                  | G3          |         |

| 60  | SD3     | D27                  | G4          |         |

| 61  | SD2     | D26                  | H1          |         |

| 62  | SD1     | D25                  | H2          |         |

| 63  | SD0     | D24                  | H3          |         |

Table 8: DNP/5280 Expansion Bus Pin Mapping to MCF5280 Pins

**Remark 1:** Please see also the Device Errata for the current version of the DNP/5280 within this documentation.

#### **DNP/5280 Memory Mapping**

| <b>Function Unit</b>   | Start Address | End Address | Access Format |

|------------------------|---------------|-------------|---------------|

| SDRAM                  | 0x0000.0000   | 0x00FF.FFFF | 32 Bits       |

| SRAM (intern)          | 0x2000.0000   | 0x2000.FFFF | 32 Bits       |

| CS1_Space              | 0x1000.0000   | 0x100F.FFFF | 8 Bits        |

| CS2_Space              | 0x1010.0000   | 0x101F.FFFF | 8 Bits        |

| CS3_Space              | 0x1020.0000   | 0x102F.FFFF | 8 Bits        |

| CS4_Space              | 0x1030.0000   | 0x103F.FFFF | 8 Bits        |

| IBSBAR                 | 0x4000.0000   | 0x7FFF.FFFF | 32 Bits       |

| Flash (MCF5282 intern) | 0xF000.0000   | 0xF007.FFFF | 32 Bits       |

| Flash                  | 0xFF80.0000   | 0xFFFF.FFFF | 16 Bits       |

**Table 9:** DNP/5280 Memory Mapping

The four memory areas called *CS1\_Space* to *CS4\_Space* are reserved for the four chip select output pins CS1, CS2, CS3 and CS4 of the DNP/5280.

The memory area called *IBSBAR* contains the MCF5280 SFRs (Special Function Registers) of the MCF5280 ColdFire MCU.

User programs are located from start address 0x0001:0000 within the DNP/5280 memory space.

### MCF5280 Chip Select Usage

| MCF5280 Pin Function | Usage                                        |

|----------------------|----------------------------------------------|

| CS0                  | Flash                                        |

| CS1                  | DNP/5280 Chip Select Output Pin CS1          |

| CS2                  | DNP/5280 Chip Select Output Pin CS2          |

| CS3                  | DNP/5280 Chip Select Output Pins CS3 and CS4 |

Table 10: MCF5280 Chip Select Usage

The DNP/5280 chip select output pins CS3 and CS4 are driven by the MCF5280 signal CS3 in combination with some address bits.

### **DNP/5280 Special Memory Areas**

The DIL/NetPC DNP/5280 default boot loader and ROM monitor program *dBUG* is using some memory space within Flash and SDRAM memory.

| <b>Function Unit</b>       | Start Address | <b>End Address</b> |

|----------------------------|---------------|--------------------|

| dBUG ROM Monitor Code Area | 0xFF80.0000   | 0xFF83.FFFF        |

| dBUG ROM Monitor Data Area | 0x0000.0000   | 0x0000.FFFF        |

Table 11: Reserved Memory Areas for the dBUG ROM Monitor

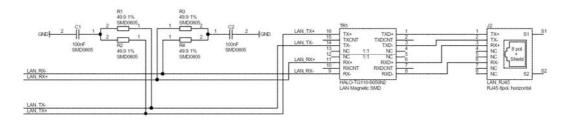

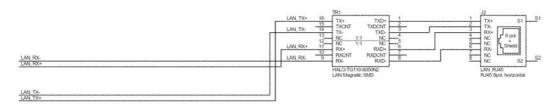

#### **External Components for the RJ45 LAN Interface**

The RJ45 Ethernet LAN interface of the DNP/5280 Rev. 1.1 (shipments until May 2004) needs some external components (four resistors and two capacitors).

Figure 4: LAN Interface for DNP/5280 Rev. 1.1

The DNP/5280 Rev. 1.2 (first shipment May 2004) offers the four resistors and two capacitors on-board. Please remove this parts from your application board.

Figure 5: LAN Interface for DNP/5280 Rev. 1.2

**Please note:** If your application board for a DIL/NetPC DNP/5280 offers the external components for DNP/5280 Rev 1.1 (Figure 4), the DNP/5280 Rev. 1.2 LAN interface don't work in this environment.

## **Device Errata**

| Problem | Remarks                                         |

|---------|-------------------------------------------------|

| RTC     | The current Linux offers no RTC driver support. |

Table 12: DNP/5280 Rev. 1.2 Device Errata

#### **Helpful Literature**

ColdFire Programmers Reference Manual R.1.0 (MCF5200PRM/AD) MCF5282 ColdFire Microcontroller User's Manual R.0.1 (MCF5282UM/D)

#### **Contact**

SSV Embedded Systems Heisterbergallee 72 D-30453 Hannover Tel. +49-(0)511-40000-0

Fax. +49-(0)511-40000-40 E-Mail: sales@ist1.de

Web: <a href="https://www.ssv-embedded.de">www.ssv-embedded.de</a>

Web: <a href="https://www.dilnetpc.com">www.dilnetpc.com</a>

#### Notes to this Document (5280RelNotes-R121E.Doc)

| Revision | Date       |                                                    | Name |

|----------|------------|----------------------------------------------------|------|

| 1.00     | 29.08.2003 | First Version in German (Rev. 1.00)                | KDW  |

| 1.10     | 02.12.2003 | Information Update for DNP/5280 Hardware Rev. 1.1  | KDW  |

| 1.11     | 21.01.2004 | Error Fixing (GPTB3 ./. GBTB2) within Table 2      | KDW  |

| 1.12     | 27.01.2004 | Translation to English                             | KDW  |

| 1.20     | 14.05.2004 | LAN Interface Change / New Device Errata           | KDW  |

| 1.21     | 19.08.2004 | MCF5280 Chip Select Usage Added, new table numbers | KDW  |

|          |            |                                                    |      |

© SSV Software Systems GmbH and Klaus-Dieter Walter 1999 – 2004. All rights reserved. No part of this documentation may be copied or reproduced in any form or by any means without the prior written consent of SSV Software Systems GmbH and Klaus-Dieter Walter. Trademarks, brands, or names included in this documentation are for identification purposes only and may be the property of others.

SSV Software Systems GmbH makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this documents nor does it make a commitment to update the information contained herein. SSV Software Systems GmbH retains the right to make changes to these specifications at any time, without notice. Contact the SSV Software Systems GmbH sales office to obtain the latest specifications before placing your order.